୧. EMC ର କାରଣ ଏବଂ ସୁରକ୍ଷା ବ୍ୟବସ୍ଥା

ହାଇ-ସ୍ପିଡ୍ ବ୍ରଶ୍ ଲେସ୍ ମୋଟରରେ, EMC ସମସ୍ୟାଗୁଡ଼ିକ ପ୍ରାୟତଃ ସମଗ୍ର ପ୍ରକଳ୍ପର କେନ୍ଦ୍ରବିନ୍ଦୁ ଏବଂ କଷ୍ଟକର ହୋଇଥାଏ, ଏବଂ ସମଗ୍ର EMCର ଅପ୍ଟିମାଇଜେସନ୍ ପ୍ରକ୍ରିୟା ବହୁତ ସମୟ ନେଇଥାଏ। ତେଣୁ, ଆମକୁ ପ୍ରଥମେ ମାନକ ଏବଂ ଅନୁରୂପ ଅପ୍ଟିମାଇଜେସନ୍ ପଦ୍ଧତିଗୁଡ଼ିକୁ ଅତିକ୍ରମ କରିବାର କାରଣଗୁଡ଼ିକୁ ସଠିକ୍ ଭାବରେ ଚିହ୍ନଟ କରିବାକୁ ପଡିବ।

EMC ଅପ୍ଟିମାଇଜେସନ୍ ମୁଖ୍ୟତଃ ତିନୋଟି ଦିଗରୁ ଆରମ୍ଭ ହୁଏ:

- ହସ୍ତକ୍ଷେପର ଉତ୍ସକୁ ଉନ୍ନତ କରନ୍ତୁ

ହାଇ-ସ୍ପିଡ୍ ବ୍ରଶ୍ଲେସ୍ ମୋଟରଗୁଡ଼ିକର ନିୟନ୍ତ୍ରଣରେ, ହସ୍ତକ୍ଷେପର ସବୁଠାରୁ ଗୁରୁତ୍ୱପୂର୍ଣ୍ଣ ଉତ୍ସ ହେଉଛି MOS ଏବଂ IGBT ଭଳି ସ୍ୱିଚ୍ ଡିଭାଇସ୍ ଦ୍ୱାରା ଗଠିତ ଡ୍ରାଇଭ୍ ସର୍କିଟ୍। ହାଇ-ସ୍ପିଡ୍ ମୋଟରର କାର୍ଯ୍ୟଦକ୍ଷତାକୁ ପ୍ରଭାବିତ ନକରି, MCU କ୍ୟାରିଅର୍ ଫ୍ରିକ୍ୱେନ୍ସିକୁ ହ୍ରାସ କରିବା, ସ୍ୱିଚ୍ ଟ୍ୟୁବ୍ର ସ୍ୱିଚ୍ ଗତିକୁ ହ୍ରାସ କରିବା ଏବଂ ଉପଯୁକ୍ତ ପାରାମିଟର ସହିତ ସ୍ୱିଚ୍ ଟ୍ୟୁବ୍ ଚୟନ କରିବା ଦ୍ୱାରା EMC ହସ୍ତକ୍ଷେପ ପ୍ରଭାବଶାଳୀ ଭାବରେ ହ୍ରାସ କରାଯାଇପାରିବ।

- ହସ୍ତକ୍ଷେପ ଉତ୍ସର ସଂଯୋଗ ପଥକୁ ହ୍ରାସ କରିବା

PCBA ରାଉଟିଂ ଏବଂ ଲେଆଉଟ୍ ଅପ୍ଟିମାଇଜ୍ କରିବା ଦ୍ଵାରା EMC ପ୍ରଭାବଶାଳୀ ଭାବରେ ଉନ୍ନତ ହୋଇପାରିବ, ଏବଂ ପରସ୍ପର ସହିତ ରେଖାଗୁଡ଼ିକର ସଂଯୋଗ ଅଧିକ ହସ୍ତକ୍ଷେପ କରିବ। ବିଶେଷକରି ଉଚ୍ଚ-ଆବୃତ୍ତି ସିଗନାଲ ରେଖା ପାଇଁ, ଲୁପ୍ ଗଠନ କରୁଥିବା ଟ୍ରେସ୍ ଏବଂ ଆଣ୍ଟେନା ଗଠନ କରୁଥିବା ଟ୍ରେସ୍ ଏଡାଇବାକୁ ଚେଷ୍ଟା କରନ୍ତୁ। ଆବଶ୍ୟକ ହେଲେ ଯୋଡକୁ ହ୍ରାସ କରିବା ପାଇଁ ସୁରକ୍ଷା ସ୍ତର ବୃଦ୍ଧି କରିପାରିବେ।

- ହସ୍ତକ୍ଷେପକୁ ଅବରୋଧ କରିବାର ଉପାୟ

EMC ଉନ୍ନତିରେ ସାଧାରଣତଃ ବିଭିନ୍ନ ପ୍ରକାରର ଇଣ୍ଡକ୍ଟନ୍ସ ଏବଂ କ୍ୟାପାସିଟର ବ୍ୟବହାର କରାଯାଏ, ଏବଂ ବିଭିନ୍ନ ହସ୍ତକ୍ଷେପ ପାଇଁ ଉପଯୁକ୍ତ ପାରାମିଟର ଚୟନ କରାଯାଏ। Y କାପାସିଟର ଏବଂ ସାଧାରଣ ମୋଡ୍ ଇଣ୍ଡକ୍ଟନ୍ସ ସାଧାରଣ ମୋଡ୍ ହସ୍ତକ୍ଷେପ ପାଇଁ, ଏବଂ X କାପାସିଟର ଭିନ୍ନ ମୋଡ୍ ହସ୍ତକ୍ଷେପ ପାଇଁ। ଇଣ୍ଡକ୍ଟନ୍ସ ଚୁମ୍ବକୀୟ ବଳୟକୁ ଏକ ଉଚ୍ଚ ଆବୃତ୍ତି ଚୁମ୍ବକୀୟ ବଳୟ ଏବଂ ଏକ ନିମ୍ନ ଆବୃତ୍ତି ଚୁମ୍ବକୀୟ ବଳୟରେ ମଧ୍ୟ ବିଭକ୍ତ କରାଯାଇଛି, ଏବଂ ଆବଶ୍ୟକ ହେଲେ ଦୁଇ ପ୍ରକାରର ଇଣ୍ଡକ୍ଟନ୍ସ ଏକ ସମୟରେ ଯୋଡାଯିବା ଆବଶ୍ୟକ।

୨. EMC ଅପ୍ଟିମାଇଜେସନ୍ କେସ୍

ଆମ କମ୍ପାନୀର 100,000-rpm ବ୍ରଶଲେସ୍ ମୋଟରର EMC ଅପ୍ଟିମାଇଜେସନ୍ରେ, ଏଠାରେ କିଛି ମୁଖ୍ୟ ବିନ୍ଦୁ ଅଛି ଯାହା ମୁଁ ଆଶା କରୁଛି ସମସ୍ତଙ୍କ ପାଇଁ ସହାୟକ ହେବ।

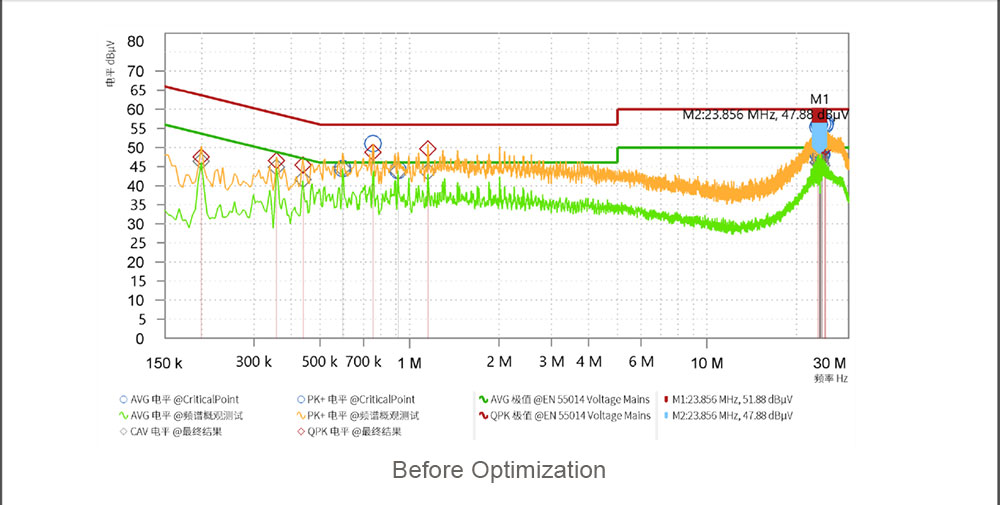

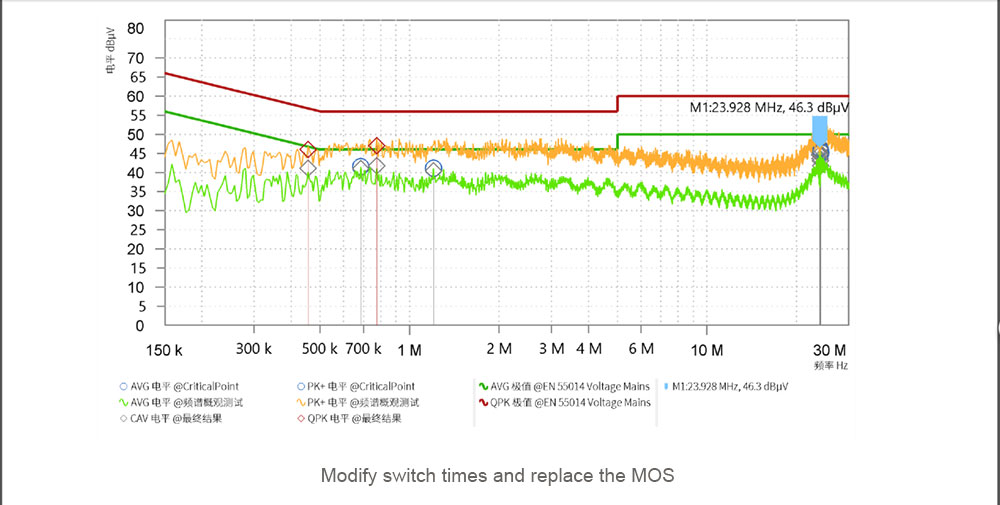

ମୋଟରକୁ ଏକ ଲକ୍ଷ ଘୂର୍ଣ୍ଣନର ଉଚ୍ଚ ଗତିରେ ପହଞ୍ଚାଇବା ପାଇଁ, ପ୍ରାରମ୍ଭିକ ବାହକ ଫ୍ରିକ୍ୱେନ୍ସି 40KHZ ରେ ସେଟ୍ କରାଯାଇଛି, ଯାହା ଅନ୍ୟ ମୋଟର ତୁଳନାରେ ଦୁଇଗୁଣ ଅଧିକ। ଏହି କ୍ଷେତ୍ରରେ, ଅନ୍ୟ ଅପ୍ଟିମାଇଜେସନ୍ ପଦ୍ଧତିଗୁଡ଼ିକ ପ୍ରଭାବଶାଳୀ ଭାବରେ EMC କୁ ଉନ୍ନତ କରିପାରି ନାହାନ୍ତି। ଏକ ଗୁରୁତ୍ୱପୂର୍ଣ୍ଣ ଉନ୍ନତି ହେବା ପୂର୍ବରୁ ଫ୍ରିକ୍ୱେନ୍ସିକୁ 30KHZ କୁ ହ୍ରାସ କରାଯାଇଛି ଏବଂ MOS ସୁଇଚିଂ ସମୟ ସଂଖ୍ୟା 1/3 ହ୍ରାସ କରାଯାଇଛି। ସେହି ସମୟରେ, ଏହା ଜଣାପଡିଲା ଯେ MOS ର ରିଭର୍ସ ଡାୟୋଡର Trrr (ରିଭର୍ସ ପୁନରୁଦ୍ଧାର ସମୟ) EMC ଉପରେ ପ୍ରଭାବ ପକାଇଥାଏ, ଏବଂ ଏକ ଦ୍ରୁତ ରିଭର୍ସ ପୁନରୁଦ୍ଧାର ସମୟ ସହିତ ଏକ MOS ଚୟନ କରାଯାଇଥିଲା। ପରୀକ୍ଷା ତଥ୍ୟ ନିମ୍ନରେ ଚିତ୍ରରେ ଦେଖାଯାଇଥିବା ପରି। 500KHZ~1MHZ ର ମାର୍ଜିନ୍ ପ୍ରାୟ 3dB ବୃଦ୍ଧି ପାଇଛି ଏବଂ ସ୍ପାଇକ୍ ତରଙ୍ଗ ଫର୍ମକୁ ସମତଳ କରାଯାଇଛି:

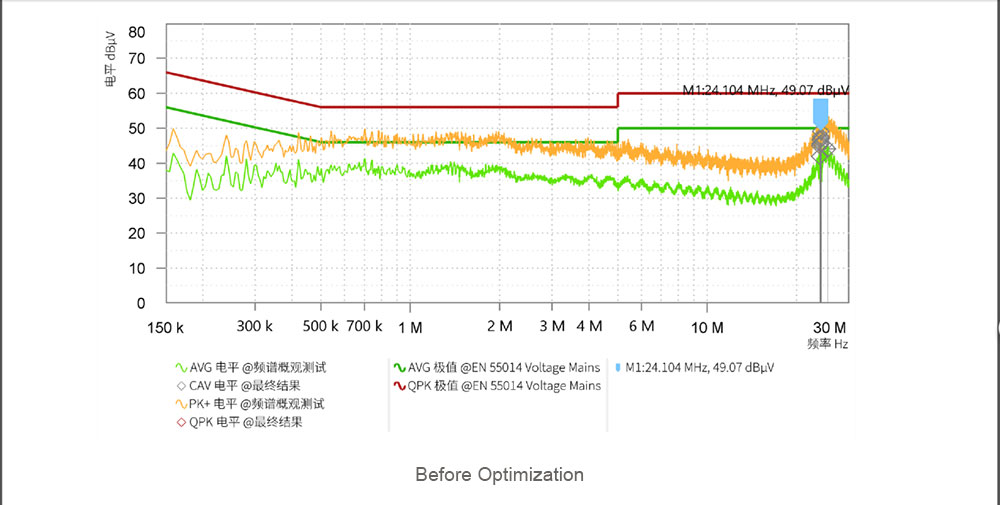

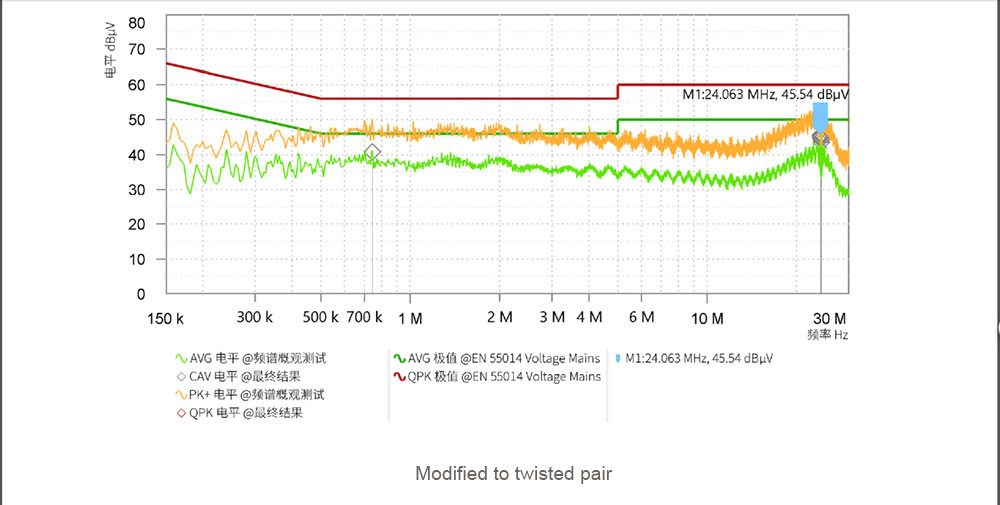

PCBA ର ସ୍ୱତନ୍ତ୍ର ଲେଆଉଟ୍ ଯୋଗୁଁ, ଦୁଇଟି ଉଚ୍ଚ-ଭୋଲଟେଜ୍ ପାୱାର ଲାଇନ ଅଛି ଯାହାକୁ ଅନ୍ୟ ସିଗନାଲ ଲାଇନ ସହିତ ଯୋଡିବାକୁ ପଡିବ। ଉଚ୍ଚ-ଭୋଲଟେଜ୍ ଲାଇନକୁ ଏକ ଟ୍ୱିଷ୍ଟ୍ ପେୟାରରେ ପରିବର୍ତ୍ତନ କରିବା ପରେ, ଲିଡ୍ ମଧ୍ୟରେ ପାରସ୍ପରିକ ହସ୍ତକ୍ଷେପ ବହୁତ କମ୍ ହୋଇଥାଏ। ପରୀକ୍ଷା ତଥ୍ୟ ନିମ୍ନରେ ଥିବା ଚିତ୍ରରେ ଦେଖାଯାଇଥିବା ପରି, ଏବଂ 24MHZ ମାର୍ଜିନ୍ ପ୍ରାୟ 3dB ବୃଦ୍ଧି ପାଇଛି:

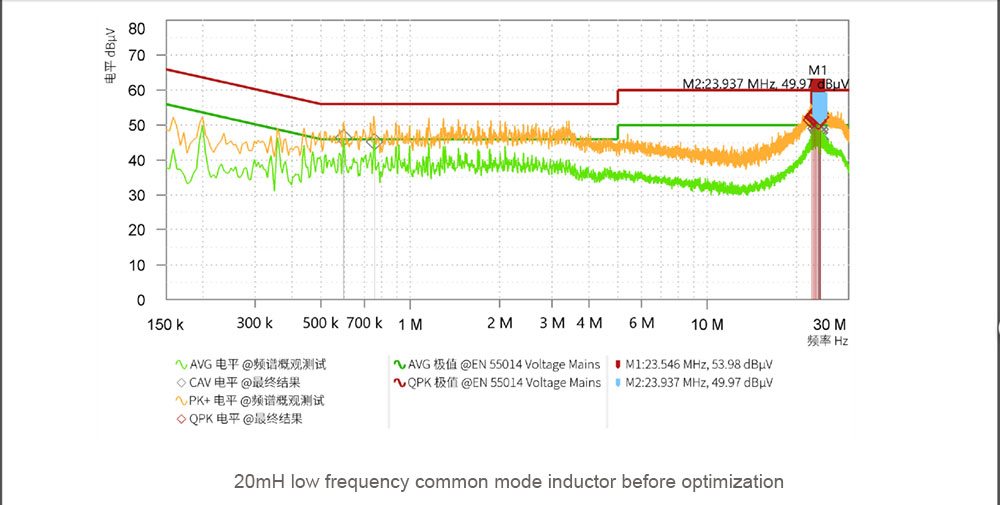

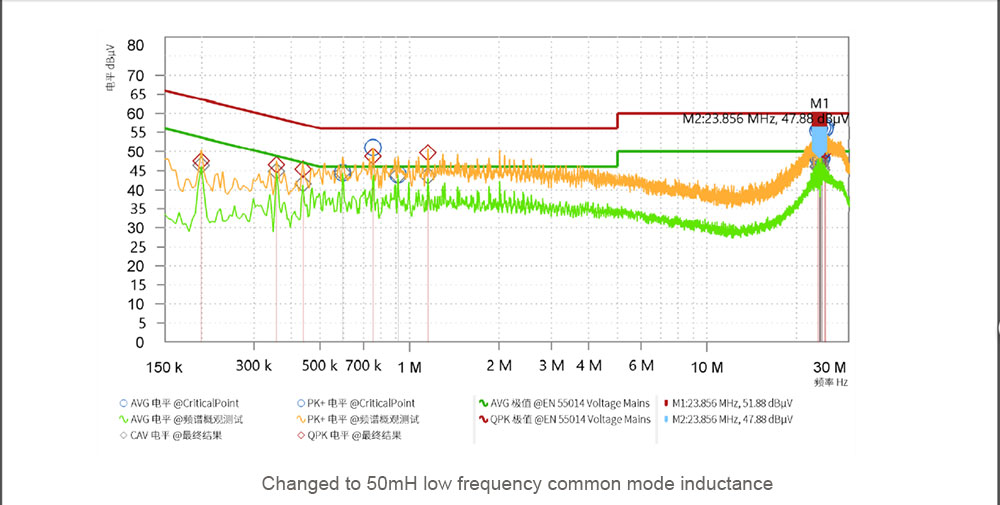

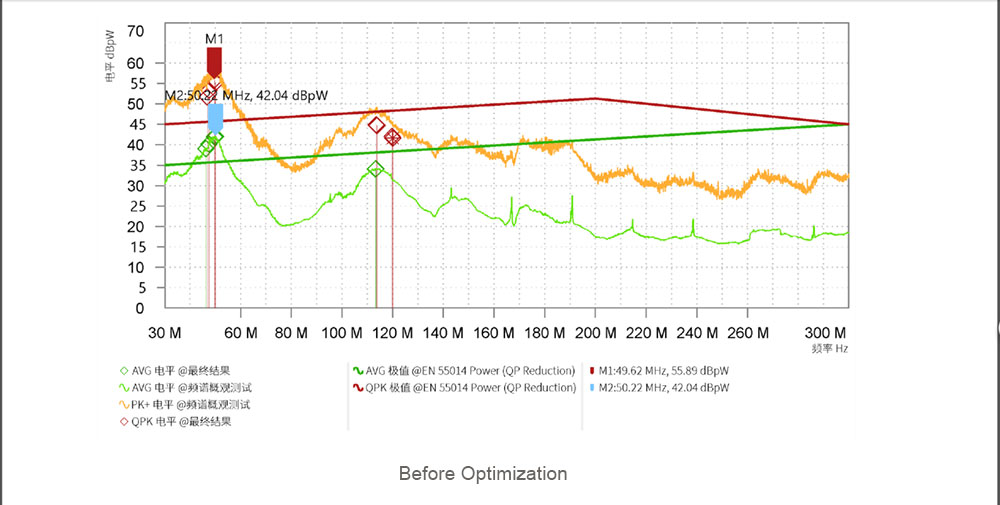

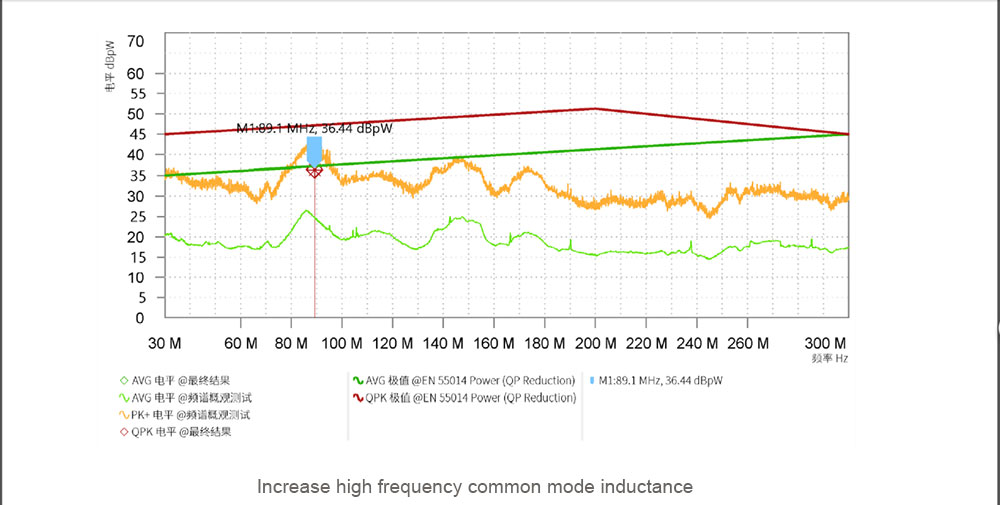

ଏହି କ୍ଷେତ୍ରରେ, ଦୁଇଟି ସାଧାରଣ-ମୋଡ୍ ଇଣ୍ଡକ୍ଟର୍ ବ୍ୟବହାର କରାଯାଏ, ଯେଉଁଥିରୁ ଗୋଟିଏ ହେଉଛି ଏକ କମ୍-ଫ୍ରିକ୍ୱେନ୍ସି ଚୁମ୍ବକୀୟ ବଳୟ, ଯାହାର ଇଣ୍ଡକ୍ଟନ୍ସ ପ୍ରାୟ 50mH, ଯାହା 500KHZ~2MHZ ପରିସର ମଧ୍ୟରେ EMCକୁ ଉଲ୍ଲେଖନୀୟ ଭାବରେ ଉନ୍ନତ କରେ। ଅନ୍ୟଟି ହେଉଛି ଏକ ଉଚ୍ଚ-ଫ୍ରିକ୍ୱେନ୍ସି ଚୁମ୍ବକୀୟ ବଳୟ, ଯାହାର ଇଣ୍ଡକ୍ଟନ୍ସ ପ୍ରାୟ 60uH, ଯାହା 30MHZ~50MHZ ପରିସର ମଧ୍ୟରେ EMCକୁ ଉଲ୍ଲେଖନୀୟ ଭାବରେ ଉନ୍ନତ କରେ।

ନିମ୍ନ-ଆବୃତ୍ତି ଚୁମ୍ବକୀୟ ବଳୟର ପରୀକ୍ଷଣ ତଥ୍ୟ ନିମ୍ନରେ ଥିବା ଚିତ୍ରରେ ଦର୍ଶାଯାଇଛି, ଏବଂ ସାମଗ୍ରିକ ମାର୍ଜିନ୍ 300KHZ~30MHZ ପରିସର ମଧ୍ୟରେ 2dB ବୃଦ୍ଧି ପାଇଛି:

ଉଚ୍ଚ-ଆବୃତ୍ତି ଚୁମ୍ବକୀୟ ବଳୟର ପରୀକ୍ଷଣ ତଥ୍ୟ ନିମ୍ନରେ ଥିବା ଚିତ୍ରରେ ଦର୍ଶାଯାଇଛି, ଏବଂ ମାର୍ଜିନ୍ 10dB ରୁ ଅଧିକ ବୃଦ୍ଧି ପାଇଛି:

ମୁଁ ଆଶା କରୁଛି ଯେ ସମସ୍ତେ EMC ଅପ୍ଟିମାଇଜେସନ୍ ଉପରେ ମତାମତ ଆଦାନପ୍ରଦାନ କରିପାରିବେ ଏବଂ ମନ୍ଥର ମନ୍ଥନ କରିପାରିବେ, ଏବଂ ନିରନ୍ତର ପରୀକ୍ଷଣରେ ସର୍ବୋତ୍ତମ ସମାଧାନ ପାଇପାରିବେ।

ପୋଷ୍ଟ ସମୟ: ଜୁନ୍-୦୭-୨୦୨୩